# **Application Note**

# LXT310/318 TO CS61310/18 REPLACEMENT GUIDE

## 1. INTRODUCTION

The purpose of this application note is to provide design suggestions and recommendations for customers wishing to replace Level One Long Haul Line Interface Units (LIUs) with the Cirrus Logic equivalents. Specifically, considerations for replacing the LXT310 T1 Long Haul LIU with the CS61310 are covered; as are considerations for replacing the LXT318 E1 Long Haul LIU with the CS61318. This document is intended to be used in conjuction with the CS61310 and CS61318 data sheets.

In short, only the resistors on the receive channel need to be changed if an LXT310 is to be replaced with a CS61310. Otherwise, all circuitry and all software remain the same. There are no changes that need to be performed if an LXT318 is to be replaced with a CS61318. Thus it is very easy to replace the LXT310/318 with Cirrus Logic's CS61310/18 equivalent parts. While the required changes are minimal, users will gain additional functionality inherent to the Cirrus Logic Crystal<sup>®</sup> line of telecommunications ICs. These additional features include:

- Crystal-less jitter attenuation

- User programmable pulse shapes

- Network loopback signal generation and detection

- Line quality, LOS and AIS monitoring in all modes

If desired, users may make use of this functionality as detailed in Section 4, *Comparisons*.

The CS61310/18 are 5.0V devices available in both PLCC and PDIP package styles, and are released to high volume production. Customer Evaluation Kits are available for these devices, part number CDB61310/318. For in-depth details regarding theory of operation, please view the respective product data sheets.

| Device #   | Description | Replaces | Package     | Power | Temp.      |  |

|------------|-------------|----------|-------------|-------|------------|--|

| CS61310-IL | T1 LH LIU   | LXT310PE | 28-pin PLCC | 5V    | Industrial |  |

| CS61310-IP | T1 LH LIU   | LXT310NE | 28-pin PDIP | 5V    | Industrial |  |

| CS61318-IL | E1 LH LIU   | LXT318PE | 28-pin PLCC | 5V    | Industrial |  |

| CS61318-IP | E1 LH LIU   | LXT318NE | 28-pin PDIP | 5V    | Industrial |  |

Table 1. Cirrus Replacements for Level One Long Haul LIUs

#### **TABLE OF CONTENTS**

| 1. | INTRODUCTION                                      | .1  |

|----|---------------------------------------------------|-----|

| 2. | BENEFITS OF FEATURES UNIQUE TO CIRRUS LOGIC       | . 3 |

| 3. | FREQUENTLY ASKED QUESTIONS                        | . 3 |

| 4. | COMPARISONS                                       | .4  |

|    | 4.1 Block Diagram: CS61310/18 Shown               |     |

|    | 4.2 Pinouts                                       | .4  |

|    | 4.2.1 T1 Pinout: CS61310 Shown                    | . 5 |

|    | 4.2.2 E1 Pinout: CS61318 Shown                    | . 6 |

|    | 4.3 Clocking                                      |     |

|    | 4.4 Application Modes                             | . 8 |

|    | 4.4.1 Hardware mode                               | . 8 |

|    | 4.4.2 Host mode                                   | . 9 |

|    | 4.5 Layout Comparisons                            |     |

|    | 4.5.1 T1 Layout Comparison: CS61310 versus LXT310 |     |

|    | 4.5.2 E1 Layout Comparison: CS61318 versus LXT318 | 11  |

|    | 4.6 Software Expansion: CS61310/18 shown          |     |

| 5. | SUMMARY                                           | 12  |

|    | 5.1 Replacing LXT310 with CS61310                 | 12  |

|    | 5.2 Replacing LXT318 with CS61318                 | 12  |

| 6. | CONCLUSION                                        | 12  |

#### LIST OF FIGURES

| Figure 1. CS61310/18 Functional Block Diagram                  | 4  |

|----------------------------------------------------------------|----|

| Figure 2. Typical Hardware-Mode Application for the CS61310/18 |    |

| Figure 3. Typical Host-Mode Application for the CS61310/18     |    |

| Figure 4. T1 Layout Comparison                                 | 10 |

| Figure 5. E1 Layout Comparison                                 |    |

#### LIST OF TABLES

| Table 1. Cirrus Replacements for Level One Long Haul LIUs             | 1   |

|-----------------------------------------------------------------------|-----|

| Table 2. Clocking options for the Cirrus and Level One Long Haul LIUs | 7   |

| Table 3. Control Registers of CS61310/61318                           | .12 |

#### **Contacting Cirrus Logic Support**

For a complete listing of Direct Sales, Distributor, and Sales Representative contacts, visit the Cirrus Logic web site at: http://www.cirrus.com/corporate/contacts/

Preliminary product information describes products which are in production, but for which full characterization data is not yet available. Advance product information describes products which are in development and subject to development charges. Cirrus Logic, Inc. has made best efforts to ensure that the information contained in this document is accurate and reliable. However, the information is subject to change without notice and is provided "AS IS" without warranty of any kind (express or implied). No responsibility is assumed by Cirrus Logic, Inc. for the use of this information, nor for infringements of patents or other rights of third parties. This document is the property of Cirrus Logic, Inc. and implies no license under patents, copyrights, trademarks, or trade secrets. No part of this publication may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical, photographic, or otherwise) without the prior written consent of Cirrus Logic, Inc. Furthermore, no part of this publication may be used as a basis for manufacture or sale of any items without the prior written consent of Cirrus Logic, Inc. The names of products of Cirrus Logic, Inc. or other vendors and suppliers appearing in this document may be trademarks or service marks of their respective owners which may be registered in some jurisdictions. A list of Cirrus Logic, Inc. trademarks and service marks can be found at http://www.cirrus.com.

### 2. BENEFITS OF FEATURES UNIQUE TO CIRRUS LOGIC

The additional functionality that a user gains by replacing the LXT310/318 with the CS61310/18 includes the following:

- Crystal-less Jitter Attenuation: This feature reduces system cost because the CS61310/18 were designed to meet stringent jitter attenuation specs without the expense of external circuitry.

- User Programmable Pulse Shapes: This feature allows the user to program the CS61310/18 to compensate for pulse degradation caused by non-standard cables, transformers, or protection circuitry. As a result, the customer saves the time and money associated with tweaking the analog hardware design to achieve T1/E1 pulse shape compliance. In some applications, this feature allows the user to reduce the T1/E1 pulse amplitude as a means to save power.

- Network Loopback Signal Generation and Detection (Loop Up/Loop Down): These features support enhanced link diagnostics and error detection without requiring human intervention at the far end.

- Line Quality, LOS and AIS Monitoring Available In All Modes: The CS61310/18's line quality monitor provides the highest line quality resolution of any LIU on the market. Consequently, the user has a much more accurate picture of the line condition. The user also has the flexibility of using either hardware or host mode to monitor the CS61310/18's LOS and AIS status.

#### 3. FREQUENTLY ASKED QUESTIONS

Is the CS61310 a drop-in replacement for the LXT310, requiring no circuit changes?

<u>ANSWER</u>: The use of the CS61310 device in a previously-LXT310 socket requires only one change. The values of the transmit resistors should be changed to 9.1  $\Omega$  from the LXT310 requirement of 12.5  $\Omega$ . In applications where common mode noise is an issue, Cirrus recommends the addition of a 0.47 µF capacitor on the receive circuit (see CS61310 datasheet).

■ Is the CS61318 a drop-in replacement for the LXT318, requiring no circuit changes?

<u>ANSWER</u>: Yes! A CS61318 device can be used in an previously LXT318 socket with NO changes to the circuit. In applications where common mode noise is an issue, Cirrus recommends the addition of a 0.47  $\mu$ F capacitor on the receive circuit (see CS61318 datasheet).

• Are there any software changes required when replacing the LXT310/318 with the CS61310/18?

<u>ANSWER</u>: No! There are NO software changes required to use the CS61310/18 in the same manner as the Level One equivalents. However, the CS61310/18 do offer additional functionality, beyond the capabilities of the respective Level One devices. If the user wishes, they can modify their software to access the features unique to Crystal Long Haul LIUs.

#### 4. COMPARISONS

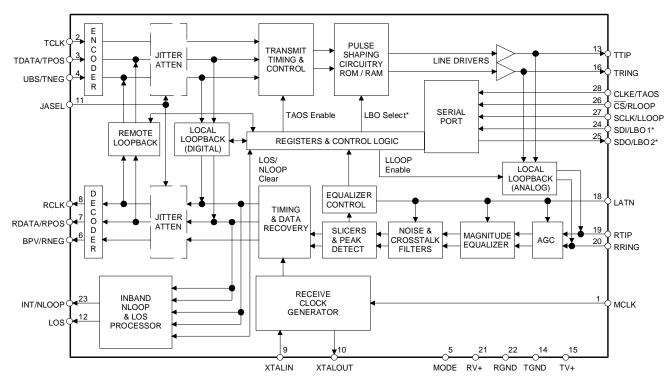

#### 4.1 Block Diagram: CS61310/18 Shown

The functional blocks internal to the CS61310/18 are shown below in Figure 1.

#### 4.2 **Pinouts**

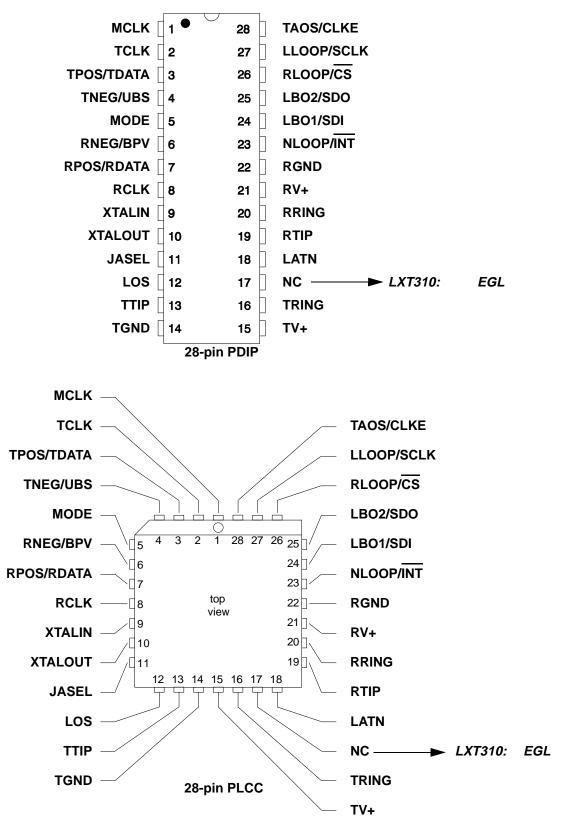

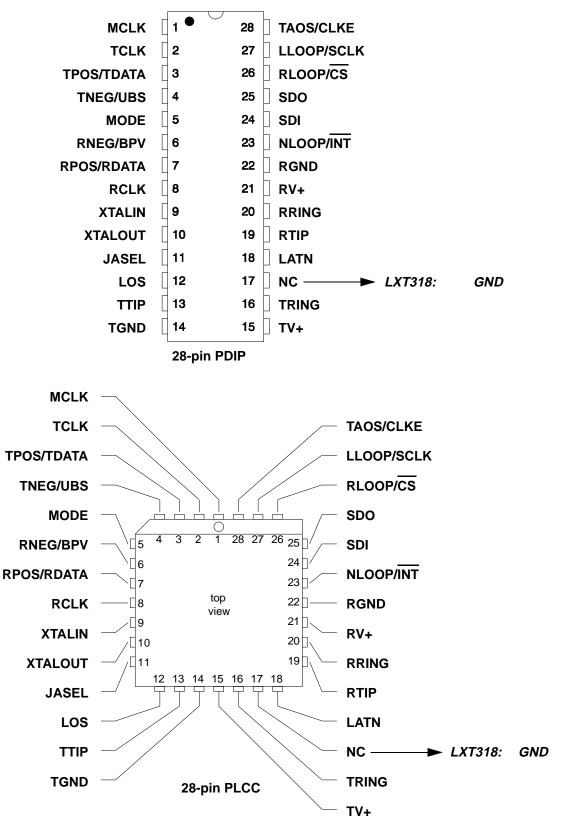

The pinout of the CS61310 differs from that of the LXT310 by one pin, pin 17. The CS61310 data sheet refers to this pin as a "No Connect", while the data sheet for the LXT310 refers to this pin as

"Equalizer Gain Limit". The LXT310 application drawings show this pin as connected to ground, which is an acceptable option for pin 17 of the CS61310.

The pinout of the CS61318 differs from that of the LXT318 by one pin, pin 17. The CS61318 data sheet refers to this pin as a "No Connect", while the data sheet for the LXT318 refers to this pin as "GND". This is an acceptable option for pin 17 of the CS61318.

\*: LBO Select, LBO1 and LBO2 only available on CS61310.

Figure 1. CS61310/18 Functional Block Diagram

#### 4.2.1 T1 Pinout: CS61310 Shown

# 4.2.2 E1 Pinout: CS61318 Shown

# 4.3 Clocking

The CS61310/18 do not require an external crystal to perform jitter attenuation. Therefore, if the devices are replacing an LXT310/318, the user has three options:

- Retain the pullable crystal required for the Level One circuit, thus making no changes,

- Replace the pullable crystal required for the Level One circuit with a non-pullable crystal, or

- Use no crystal, so long as an external system clock is provided via MCLK.

| Available Clock Sources                                           | CS61310/CS61318                                                                      | LXT310/LXT318                                                                                                                        |  |  |  |

|-------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                   | MCLK at 1X bit rate                                                                  | MCLK at 1X bit rate                                                                                                                  |  |  |  |

|                                                                   | Drives Receiver and Jitter Attenuator through MCLK                                   | Drives Receiver through MCLK                                                                                                         |  |  |  |

|                                                                   | External crystal is ignored if transitions detected on MCLK                          | MCLK actively selected if XTALIN is grounded                                                                                         |  |  |  |

| Reference provided by exter-<br>nal source (through MCLK)<br>only | Ground XTALIN to enable Jitter Atten-<br>uator                                       | Jitter Attenuator actively disabled if<br>XTALIN pulled up and XTALOUT left<br>open (Note: JA not available if xtal not<br>provided) |  |  |  |

|                                                                   | Purity of external clock determines<br>maximum performance of Jitter Atten-<br>uator | N/A - Jitter Attenuator not available                                                                                                |  |  |  |

|                                                                   | Transmitter driven through TCLK                                                      | Transmitter driven through TCLK                                                                                                      |  |  |  |

|                                                                   | Crystal at 4X bit rate                                                               | Crystal at 4X bit rate                                                                                                               |  |  |  |

| Reference provided by exter-                                      | Non-pullable                                                                         | Pullable                                                                                                                             |  |  |  |

| nal crystal (through XTA-<br>LIN/OUT) only                        | Drives Receiver and Jitter Attenuator through XTALIN, XTALOUT                        | Drives Receiver and Jitter Attenuator through XTALIN, XTALOUT                                                                        |  |  |  |

|                                                                   | Drive TCLK from external source; can be connected to RCLK                            | Drive TCLK from external source; can be connected to RCLK                                                                            |  |  |  |

| References provided to both<br>MCLK and XTALIN/OUT                | Only MCLK will be used                                                               | Use external clock to drive Receiver<br>and Transmitter; crystal required to<br>drive Jitter Attenuator                              |  |  |  |

Table 2. Clocking options for the Cirrus and Level One Long Haul LIUs

#### 4.4 Application Modes

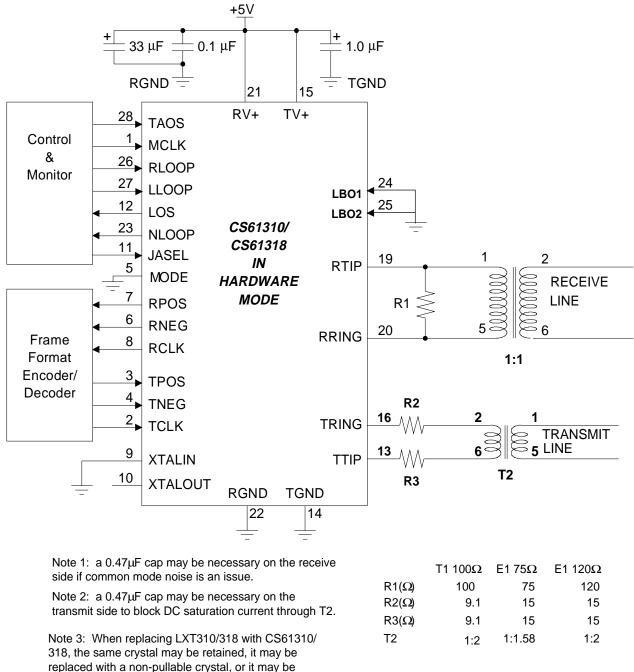

#### 4.4.1 Hardware mode

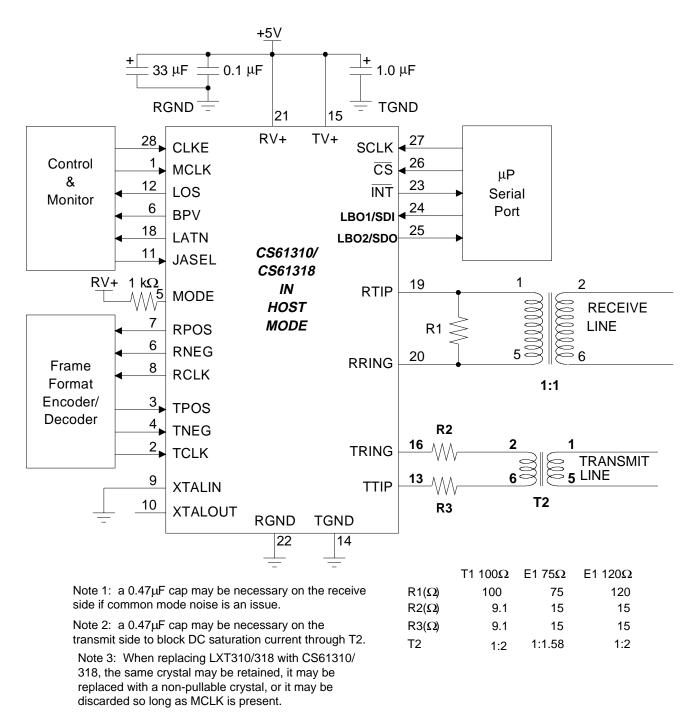

The following layout is a typical hardware-mode application for the CS61310/18.

discarded so long as MCLK is present.

Figure 2. Typical Hardware-Mode Application for the CS61310/18

AN164

#### 4.4.2 Host mode

The following layout is a typical host-mode application for the CS61310/18.

Figure 3. Typical Host-Mode Application for the CS61310/18

AN164

### 4.5 Layout Comparisons

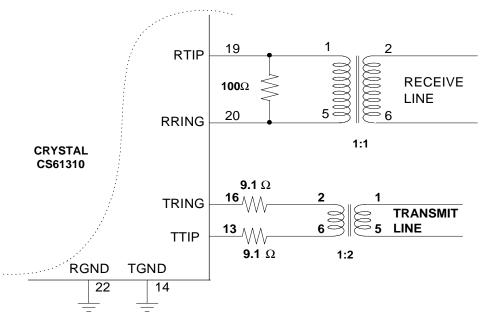

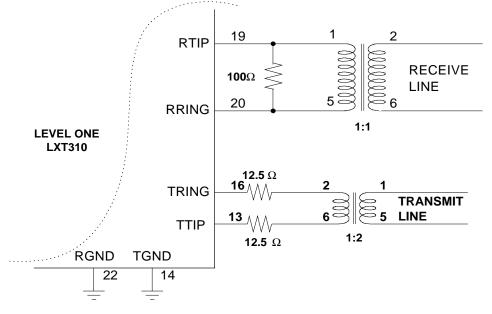

### 4.5.1 T1 Layout Comparison: CS61310 versus LXT310

The following partial schematics detail the minor difference in T1 layouts.

Notes:

A 0.47 $\mu$ F capacitor to ground may be necessary on the receive side if common mode noise is an issue. See the CS61310 data sheet.

A 0.47µF capacitor may be necessary in series with one of the transmit matching resistors to block DC saturation current. See the CS61310 data sheet.

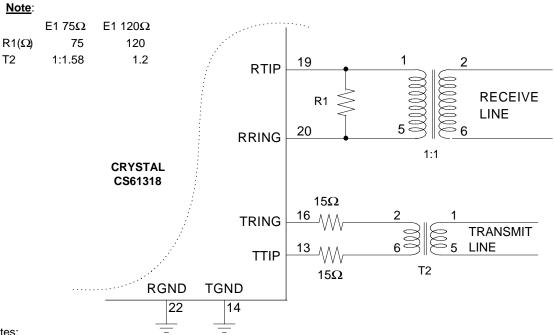

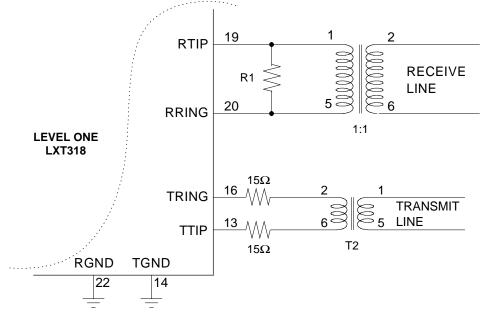

#### 4.5.2 E1 Layout Comparison: CS61318 versus LXT318

The following partial schematics emphasize that there are no differences in E1 layout.

Notes:

A 0.47µF capacitor to ground may be necessary on the receive side if common mode noise is an issue. See the CS61318 data sheet.

A 0.47µF capacitor may be necessary in series with one of the transmit matching resistors to block DC saturation current. See the CS61318 data sheet.

# 4.6 Software Expansion: CS61310/18 shown

The register set of the CS61310/18 is shown below. The Level One equivalent devices provide only a register comparable to CR1 in the CS61310/18. If a user wishes to make use of the additional functionality of the Cirrus Logic devices, it is recommended that the system software be modified to accommodate the additional registers. A complete description of the registers, their functions, and the clock edges upon which serial data is valid may be found in the respective product data sheets.

# 5. SUMMARY

### 5.1 Replacing LXT310 with CS61310

- **•** Replace  $12.5\Omega$  Transmit resistors with  $9.1\Omega$

- Leave Pin 17 tied to GND, or disconnect

- Keep pullable crystal, replace with non-pullable, or remove

- Enable or disable jitter attenuator per Clocking table

- Implement additional software registers, as desired

#### 5.2 Replacing LXT318 with CS61318

- Leave Pin 17 tied to GND, or disconnect

- Keep pullable crystal, replace with non-pullable, or remove

- Enable or disable jitter attenuator per Clocking table

- Implement additional software registers, as desired

#### 6. CONCLUSION

It is extremely easy to replace the Level One Long Haul LIUs with the Cirrus equivalents. In doing so, users will gain additional functionality (should they wish to make use of it) and will reduce their BOM costs by eliminating the external crystal should they so desire. Design assistance is available from expert engineers at Cirrus Logic. For further information, please contact your local Cirrus representative, call 800-888-5016 or email tcomm@crystal.cirrus.com.

|                             | 7    | 6       | 5        | 4                 | 3                 | 2         | 1     | 0        | ADDR        |

|-----------------------------|------|---------|----------|-------------------|-------------------|-----------|-------|----------|-------------|

| Control Register 1<br>(CR1) | TAOS | LLOOP   | RLOOP    | LBO2 <sup>a</sup> | LBO1 <sup>b</sup> | CODER TAZ | NLOOP | LOS      | 0x10<br>R/W |

| Control Register 2<br>(CR2) | AIS  | RAMPLSE | RSVD = 0 | LOOPDN            | LOOPUP            | RPWDN     | TxHIZ | RSVD = 0 | 0x11<br>R/W |

| Equalizer Gain<br>(EQGAIN)  | х    | Х       | х        | EQ4               | EQ3               | EQ2       | EQ1   | EQ0      | 0x12 R      |

| RAM Address<br>(RAM)        | MSB  | -       | -        | -                 | -                 | -         | -     | LSB      | 0x13<br>R/W |

| Reserved<br>(Set to "0")    | 0    | 0       | 0        | 0                 | 0                 | 0         | 0     | 0        | 0x14        |

#### Table 3. Control Registers of CS61310/61318

a.Bit 4 of CR1 is reserved (RSVD=0) on the CS61318. b.Bit 3of CR1 is reserved (RSVD=0) on the CS61318.

# • Notes •